# Product Preview

# High Performance Resonant Mode Controller featuring High-voltage Drivers

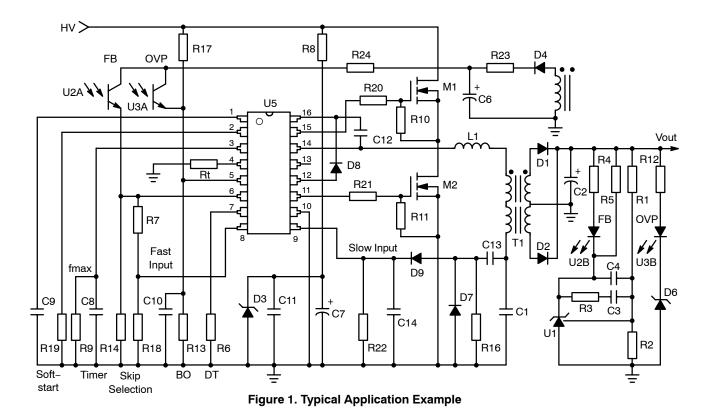

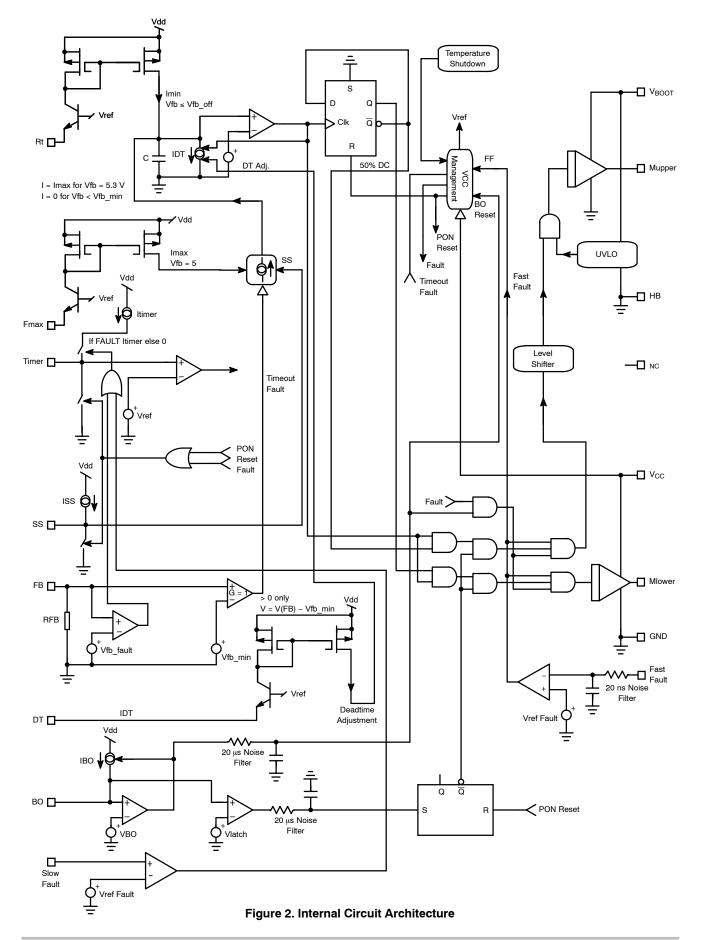

The NCP1396 A/B offers everything needed to build a reliable and rugged resonant mode power supply. Its unique architecture includes a 500 kHz Voltage Controller Oscillator whose control mode brings flexibility when an ORing function is a necessity, e.g. in multiple feedback paths implementations. Thanks to its proprietary high–voltage technology, the controller welcomes a bootstrapped MOSFET driver for half–bridge applications accepting bulk voltages up to 600 V. Protections featuring various reaction times, e.g. immediate shutdown or timer–based event, brown–out, broken opto–coupler detection etc., contribute to a safer converter design, without engendering additional circuitry complexity. An adjustable deadtime also helps lowering the shoot–through current contribution as the switching frequency increases.

#### Features

- High-frequency Operation from 50 kHz up to 500 kHz

- 600 V High-voltage Floating Driver

- Selectable Minimum Switching Frequency with ±3% Accuracy

- Adjustable Deadtime from 100 ns to 2 µs.

- Startup Sequence via an Adjustable Soft-start

- Brown-out Protection for a Simpler PFC Association

- Latched Input for Severe Fault Conditions, e.g. Over Temperature or OVP

- Timer-based Input with Auto-recovery Operation for Delayed Event Reaction

- Enable Input for Immediate Event Reaction or Simple ON/OFF Control

- $V_{CC}$  Operation up to 20 V

- Low Startup Current of 300 µA

- 1 A / 0.5 A Peak Current Sink / Source Drive Capability

- Common Collector Optocoupler Connection for Easier ORing

- Internal Temperature Shutdown

- B Version features 10 V V<sub>CC</sub> Startup Threshold

- SO16 or DIP16 Package

#### **Typical Applications**

- Flat Panel Display Power Converters

- High Power AC/DC Adapters for Notebooks

- Industrial and Medical Power Sources

- Offline Battery Chargers

# **ON Semiconductor®**

http://onsemi.com

#### **ORDERING INFORMATION**

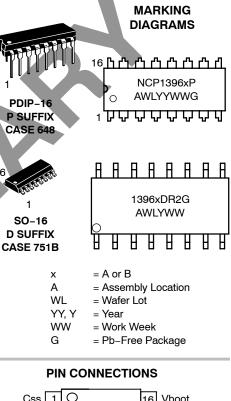

See detailed ordering and shipping information in the package dimensions section on page 24 of this data sheet.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

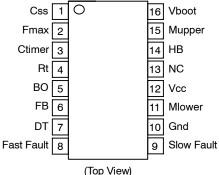

#### **Pin Function Description**

| Pin No. | Pin Name   | Function                | Pin Description                                                                                             |

|---------|------------|-------------------------|-------------------------------------------------------------------------------------------------------------|

| 1       | Css        | Soft-start              | Select the soft-start duration                                                                              |

| 2       | Fmax       | Frequency clamp         | A resistor sets the maximum frequency excursion                                                             |

| 3       | Ctimer     | Timer duration          | Sets the timer duration in presence of a fault                                                              |

| 4       | Rt         | Timing resistor         | Connecting a resistor to this pin, sets the minimum oscillator frequency reached for VFB = 1 V $$           |

| 5       | BO         | Brown-Out               | Detects low input voltage conditions. When brought above Vlatch, it fully latches off the controller.       |

| 6       | FB         | Feedback                | Injecting current in this pin increases the oscillation frequency up to Fmax.                               |

| 7       | DT         | Dead-time               | A simple resistor adjusts the dead-time width                                                               |

| 8       | Fast Fault | Quick fault detection   | Fast shut-down pin. Upon release, a clean startup sequence occurs. Can be used for skip cycle purposes.     |

| 9       | Slow Fault | Slow fault detection    | When asserted, the timer starts to countdown and shuts down the controller at the end of its time duration. |

| 10      | Gnd        | Analog ground           | -                                                                                                           |

| 11      | Mlower     | Low side output         | Drives the lower side MOSFET                                                                                |

| 12      | Vcc        | Supplies the controller | The controller accepts up to 20 V                                                                           |

| 13      | NC         | Not connected           | Increases the creepage distance                                                                             |

| 14      | HB         | Half-bridge connection  | Connects to the half-bridge output                                                                          |

| 15      | Mupper     | High side output        | Drives the higher side MOSFET                                                                               |

| 16      | Vboot      | Bootstrap pin           | The floating $V_{CC}$ supply for the upper stage                                                            |

#### **Maximum Ratings**

| Rating                                                              | Symbol            | Value                         | Unit |

|---------------------------------------------------------------------|-------------------|-------------------------------|------|

| High Voltage bridge pin, pin 14                                     | VBRIDGE           | -1 to 600                     | V    |

| Floating supply voltage, ground referenced                          | VBOOT-<br>VBRIDGE | 0 to 20                       | V    |

| High side output voltage                                            | VDRV_HI           | VBRIDGE-0.3 to<br>VBOOT+0.3   | V    |

| Low side output voltage                                             | VDRV_LO           | -0.3 to V <sub>CC</sub> + 0.3 | V    |

| Allowable output slew rate                                          | dVBRIDGE/dt       | 50                            | V/ns |

| Power Supply voltage, pin 12                                        | Vcc               | 20                            | V    |

| Maximum voltage, all pins (except pin 11 and 10)                    | -                 | -0.3 to 10                    | V    |

| Thermal Resistance – Junction-to-Air, PDIP version                  | $R_{	heta JA}$    | 100                           | °C/W |

| Thermal Resistance – Junction-to-Air, SOIC version                  | R <sub>0JA</sub>  | 130                           | °C/W |

| Storage Temperature Range                                           | _                 | -60 to +150                   | °C   |

| ESD Capability, HBM model (All pins except $V_{\mbox{CC}}$ and HV)  | _                 | 2                             | kV   |

| ESD Capability, Machine Model (All pins except pin 11 - see Note 1) | _                 | 200                           | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

This device series contains ESD protection and exceeds the following tests: Human Body Model 2000 V per Mil–Std–883, Method 3015 Machine Model Method 200 V

ESD Capability, Machine Model for pin 11 is 180 V.

2. This device meets latch-up tests defined by JEDEC Standard JESD78.

#### **ELECTRICAL CHARACTERISTICS**

(For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = 0^{\circ}C$  to  $+125^{\circ}C$ , Max  $T_J = 150^{\circ}C$ ,  $V_{CC} = 12$  V, unless otherwise noted.)

| Characteristic                                                                                                 | Pin             | Symbol                 | Min  | Тур  | Max  | Unit        |

|----------------------------------------------------------------------------------------------------------------|-----------------|------------------------|------|------|------|-------------|

| SUPPLY SECTION                                                                                                 | • •••           | Cymbol                 |      | 176  | Ших  | onit        |

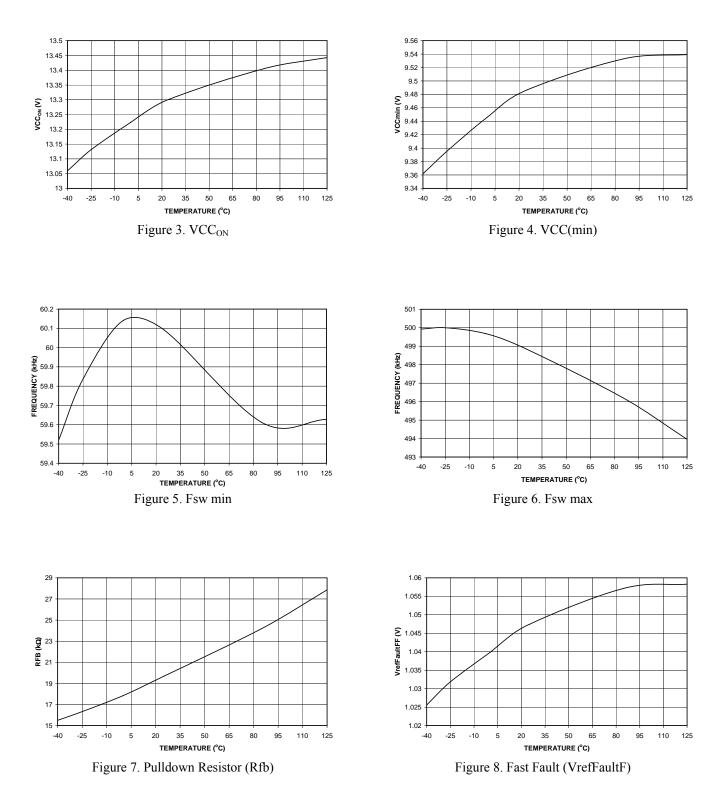

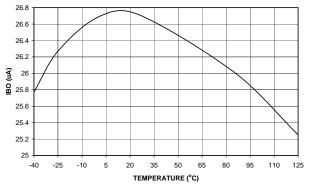

| Turn-on threshold level, Vcc going up – A version                                                              | 12              | VCC <sub>ON</sub>      | 12.3 | 13.3 | 14.3 | V           |

| Turn-on threshold level, Vcc going up – B version                                                              | 12              | VCC <sub>ON</sub>      | 9.5  | 10.5 | 11.5 | v           |

| Minimum operating voltage after turn-on                                                                        |                 | VCC <sub>(min)</sub>   | 8.5  | 9.5  | 10.5 | V           |

| Startup voltage on the floating section                                                                        | 12<br>16–14     | Vboot <sub>ON</sub>    | 8    | 9    | 10.0 | V           |

| Cutoff voltage on the floating section                                                                         | 16–14           | Vboot <sub>(min)</sub> | 7.4  | 8.4  | 9.4  | V           |

| Startup current, Vcc < VCC <sub>ON</sub>                                                                       | 10=14           | Istartup               | -    | -    | 300  | μA          |

| Vcc level at which the internal logic gets reset                                                               | 12              | VCC <sub>reset</sub>   |      | 6.5  |      | μ<br>Λ<br>V |

| Internal IC consumption, no output load on pin 15/14 – 11/10, Fsw =                                            | 12              | ICC1                   |      | 4    |      | mA          |

| 300 kHz                                                                                                        | 12              | 1001                   | -    | 4    | -    | IIIA        |

| Internal IC consumption, 1 nF output load on pin 15/14 – 11/10, Fsw = 300 kHz                                  | 12              | ICC2                   | -    | 11   | -    | mA          |

| Consumption in fault mode (All drivers disabled, $V_{CC} > V_{CC(min)}$ )                                      | 12              | ICC3                   | -    | 1.2  | -    | mA          |

| VOLTAGE CONTROL OSCILLATOR (VCO)                                                                               |                 |                        |      |      |      |             |

| Characteristic                                                                                                 | Pin             | Symbol                 | Min  | Тур  | Max  | Unit        |

| Minimum switching frequency, Rt = 18 k $\Omega$ on pin 4, Vpin 6 = 0.8 V, DT = 300 ns                          |                 | Fsw min                | 58.2 | 60   | 61.8 | kHz         |

| Maximum switching frequency, Rfmax = 1.3 k $\Omega$ on pin 2, Vpin 6 > 5.3 V, Rt = 18 k $\Omega$ , DT = 300 ns |                 | Fsw max                | 425  | 500  | 575  | kHz         |

| Feedback pin swing above which $\Delta f = 0$                                                                  | 6               | FBSW                   | -    | 5.3  | -    | V           |

| Operating duty-cycle symetry                                                                                   |                 | DC                     | 48   | 50   | 52   | %           |

| Delay before any driver re-start in fault mode                                                                 |                 | Tdel                   | -    | 20   | -    | μs          |

| FEEDBACK SECTION                                                                                               |                 |                        |      |      |      |             |

| Characteristic                                                                                                 | Pin             | Symbol                 | Min  | Тур  | Max  | Unit        |

| Internal pull-down resistor                                                                                    | 6               | Rfb                    | -    | 20   | -    | kΩ          |

| Voltage on pin 6 below which the FB level has no VCO action                                                    | 6               | Vfb_min                | -    | 1.2  | -    | V           |

| Voltage on pin 6 below which the controller considers a fault                                                  | 6               | Vfb_off                | -    | 0.6  | -    | V           |

| DRIVE OUTPUT                                                                                                   | •               |                        |      |      | •    |             |

| Characteristic                                                                                                 | Pin             | Symbol                 | Min  | Тур  | Max  | Unit        |

| Output voltage rise-time @ CL = 1 nF, 10-90% of output signal                                                  |                 | T <sub>r</sub>         | -    | 40   | -    | ns          |

| Output voltage fall-time @ CL = 1 nF, 10-90% of output signal                                                  |                 | T <sub>f</sub>         | -    | 20   | -    | ns          |

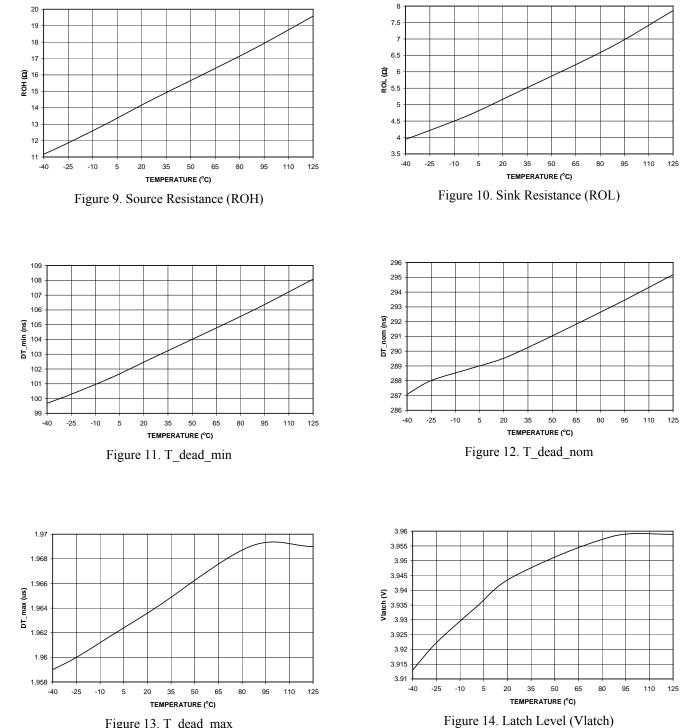

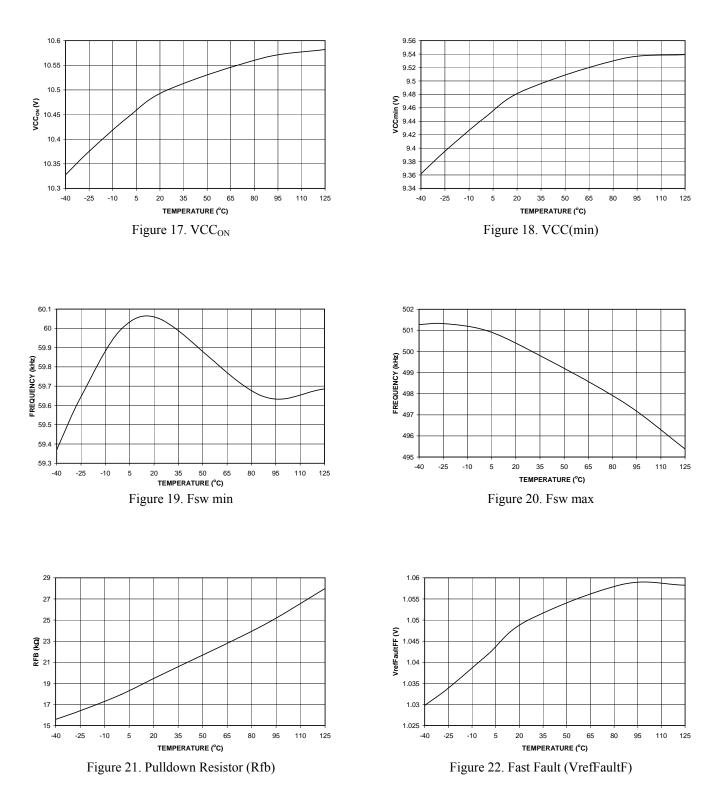

| Source resistance                                                                                              | 15–14/1<br>1–10 | R <sub>OH</sub>        | _    | 13   | -    | Ω           |

| Sink resistance                                                                                                | 15–14/1<br>1–10 | R <sub>OL</sub>        | _    | 5.5  | -    | Ω           |

| Dead time with $R_{DT}$ = 10 k $\Omega$ from pin 7 to GND                                                      | 7               | T_dead                 | 250  | 300  | 340  | ns          |

| Maximum dead-time with $R_{DT}$ = 82 k $\Omega$ from pin 7 to GND                                              | 7               | T_dead-max             | -    | 2    | -    | μs          |

| Minimum dead-time, $R_{DT}$ = 3 k $\Omega$ from pin 7 to GND                                                   | 7               | T_dead-min             | -    | 100  | -    | ns          |

| Leakage current on high voltage pins to GND                                                                    | 14,<br>15,16    | IHV_LEAK               | _    | -    | 5    | μΑ          |

|                                                                                                                |                 | •                      |      |      |      | •           |

3. The A version does not activate soft-start (unless the feedback pin voltage is below 0.6 V) when the fast-fault is released, this is for skip cycle implementation. The B version does activate the soft-start upon release of the fast-fault input for any feedback conditions. 4. Guaranteed by design

#### **ELECTRICAL CHARACTERISTICS**

(For typical values  $T_J = 25^{\circ}C$ , for min/max values  $T_J = 0^{\circ}C$  to  $+125^{\circ}C$ , Max  $T_J = 150^{\circ}C$ ,  $V_{CC} = 12$  V, unless otherwise noted.)

| Characteristic                                                             | Pin | Symbol    | Min | Тур | Max | Unit |  |

|----------------------------------------------------------------------------|-----|-----------|-----|-----|-----|------|--|

| Timer charge current                                                       | 3   | ltimer    | -   | 160 | -   | μA   |  |

| Timer duration with a 1 $\mu\text{F}$ capacitor and a 1 $M\Omega$ resistor | 3   | T-timer   | -   | 25  | -   | ms   |  |

| Timer recurrence in permanent fault, same values as above                  | 3   | T-timerR  | -   | 1.4 | -   | s    |  |

| Voltage at which pin 3 stops output pulses                                 | 3   | VtimerON  | 3.5 | 4   | 4.4 | V    |  |

| Voltage at which pin 3 re-starts output pulses                             | 3   | VtimerOFF | 0.9 | 1   | 1.1 | V    |  |

| Soft-start ending voltage                                                  | 1   | VSS       | -   | 2   | -   | V    |  |

| Soft-start charge current                                                  | 1   | ISS       | 80  | 105 | 125 | μA   |  |

| Soft-start duration with a 100 nF capacitor (Note 3)                       | 1   | T-SS      | -   | 1.8 | -   | ms   |  |

| PROTECTION                                                                 |     |           |     |     |     |      |  |

| Characteristic                                                             | Pin | Symbol    | Min | Тур | Max | Unit |  |

| Characteristic                                        | Pin | Symbol      | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------|-----|-------------|------|------|------|------|

| Reference voltage for fast input (Note 4)             | 8–9 | VrefFaultF  | 1.00 | 1.05 | 1.10 | V    |

| Hysteresis for fast input (Note 4)                    | 8–9 | HysteFaultF | -    | 80   | -    | mV   |

| Reference voltage for slow input                      | 8–9 | VrefFaultS  | 0.95 | 1.00 | 1.05 | V    |

| Hysteresis for slow input                             | 8–9 | HysteFaultS | -    | 60   | -    | mV   |

| Propagation delay for fast fault input drive shutdown | 8   | TpFault     | -    | 55   | 90   | ns   |

| Brown-Out input bias current                          | 5   | IBObias     | -    | 0.02 | -    | μΑ   |

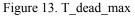

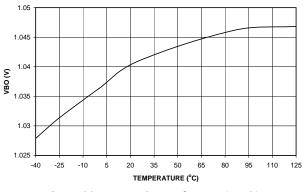

| Brown-Out level (Note 4)                              | 5   | VBO         | 0.99 | 1.04 | 1.09 | V    |

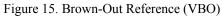

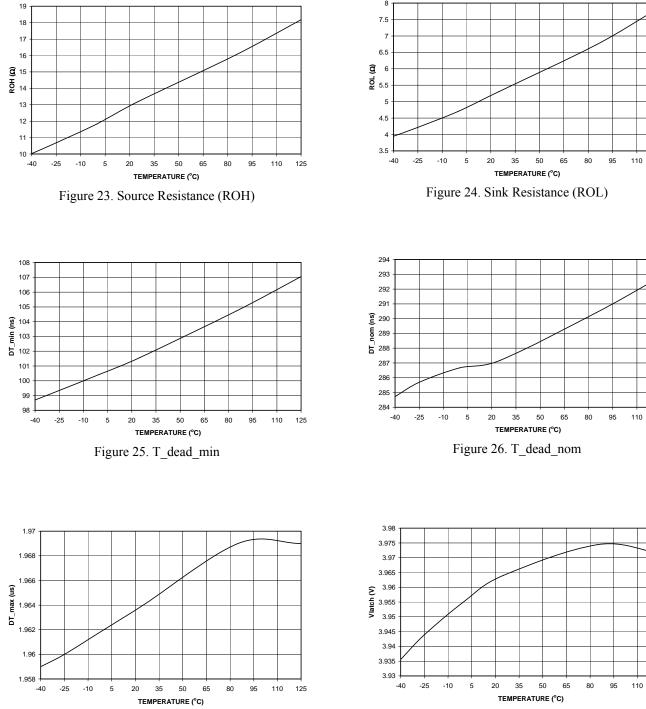

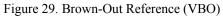

| Hysteresis current, Vpin5 > VBO – A version           | 5   | IBO_A       | 21.5 | 26.5 | 31.5 | μA   |

| Hysteresis current, Vpin5 > VBO – B version           | 5   | IBO_B       | 86   | 106  | 126  | μΑ   |

| Latching voltage                                      | 5   | Vlatch      | 3.6  | 4    | 4.4  | V    |

| Temperature shutdown                                  | -   | TSD         | 140  | -    | -    | °C   |

| Hysteresis                                            | -   | TSDhyste    | Ι    | 30   | -    | °C   |

3. The A version does not activate soft-start (unless the feedback pin voltage is below 0.6 V) when the fast-fault is released, this is for skip cycle implementation. The B version does activate the soft-start upon release of the fast-fault input for any feedback conditions.Guaranteed by design

#### **TYPICAL CHARACTERISTICS – A VERSION**

http://onsemi.com 8

Figure 16. Brown-Out Hysteresis Current (IBO)

#### **TYPICAL CHARACTERISTICS – B VERSION**

8

Figure 28. Latch Level (Vlatch)

125

125

125

Figure 27. T\_dead\_max

Figure 30. Brown-Out Hysteresis Current (IBO)

# **Application information**

The NCP1396 A/B includes all necessary features to help building a rugged and safe switch-mode power supply featuring an extremely low standby power. The below bullets detail the benefits brought by implementing the NCP1396 controller:

- *Wide frequency range*: A high-speed Voltage Control Oscillator allows an output frequency excursion from 50 kHz up to 500 kHz on Mlower and Mupper outputs.

- *Adjustable dead-time*: Thanks to a single resistor wired to ground, the user has the ability to include some dead-time, helping to fight cross-conduction between the upper and the lower transistor.

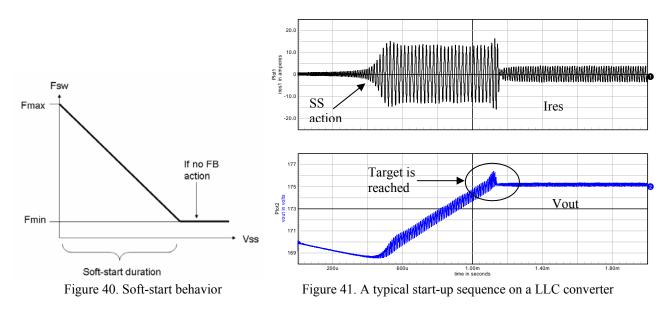

- *Adjustable soft-start*: Every time the controller starts to operate (power on), the switching frequency is pushed to the programmed maximum value and slowly moves down toward the minimum frequency, until the feedback loop closes. The soft-start sequence is activated in the following cases: a) normal startup b) back to operation from an off state: during hiccup faulty mode, brown-out or temperature shutdown (TSD). In the NCP1396A, the soft-start is not activated back to operation from the fast fault input, unless the feedback pin voltage is below 0.6 V. To the opposite, in the B version, the soft-start is always activated back from the fast fault input whatever the feedback level is.

- Adjustable minimum and maximum frequency excursion: In resonant applications, it is important to stay away from the resonating peak to keep operating the converter in the right region. Thanks to a single external resistor, the designer can program its lowest frequency point, obtained in lack of feedback voltage (during the startup sequence or in short-circuit conditions). Internally trimmed capacitors offer a  $\pm 3\%$  precision on the selection of the minimum switching frequency. The adjustable upper stop being less precise to  $\pm 15\%$ .

- *Low startup current*: When directly powered from the high-voltage DC rail, the device only requires 300 µA to start-up. In case of an auxiliary supply, the B version offers a lower start-up threshold to cope with a 12 V dc rail.

- **Brown-Out detection**: To avoid operation from a low input voltage, it is interesting to prevent the controller from switching if the high-voltage rail is not within the right boundaries. Also, when teamed with a PFC front-end circuitry, the brown-out detection can ensure a clean start-up sequence with soft-start, ensuring that the PFC is stabilized before energizing the resonant tank. The A version features a 27 µA

hysteresis current for the lowest consumption and the B version slightly increases this current to 100  $\mu$ A in order to improve the noise immunity.

- Adjustable fault timer duration: When a fault is detected on the slow fault input or when the FB path is broken, a timer starts to charge an external capacitor. If the fault is removed, the timer opens the charging path and nothing happens. When the timer reaches its selected duration (via a capacitor on pin 3), all pulses are stopped. The controller now waits for the discharge via an external resistor of pin 3 capacitor to issue a new clean startup sequence with soft-start.

- *Cumulative fault events*: In the NCP1396A/B, the timer capacitor is not reset when the fault disappears. It actually integrates the information and cumulates the occurrences. A resistor placed in parallel with the capacitor will offer a simple way to adjust the discharge rate and thus the auto-recovery retry rate.

- *Fast and slow fault detection*: In some application, subject to heavy load transients, it is interesting to give a certain time to the fault circuit, before activating the protection. On the other hands, some critical faults cannot accept any delay before a corrective action is taken. For this reason, the NCP1396A/B includes a fast fault and a slow fault input. Upon assertion, the fast fault immediately stops all pulses and stays in the position as long as the driving signal is high. When released low (the fault has gone), the controller has several choices: in the A version, pulses are back to a level imposed by the feedback pin without soft-start, but in the B version, pulses are back through a regular soft-start sequence.

- *Skip cycle possibility*: The absence of soft-start on the NCP1396A fast fault input offers an easy way to implement skip cycle when power saving features are necessary. A simple resistive connection from the feedback pin to the fast fault input, and skip can be implemented.

- **Broken feedback loop detection**: Upon start-up or any time during operation, if the FB signal is missing, the timer starts to charge a capacitor. If the loop is really broken, the FB level does not grow-up before the timer ends counting. The controller then stops all pulses and waits that the timer pin voltage collapses to 1V typically before a new attempt to re-start, via the soft-start. If the optocoupler is permanently broken, a hiccup takes place.

- *Finally, two circuit versions, A and B*: The A and B versions differ because of the following changes:

- 1. The startup thresholds are different, the A starts to pulse for Vcc = 13.3 V whereas the B pulses for Vcc = 10.5 V. The turn off levels are the same however. The A is recommended for consumer products where the designer can use an external startup resistor, whereas the B is more recommended for industrial / medical applications where a 12 V auxiliary supply directly powers the chip.

- 2. The A version does not activate the soft-start upon release of the fast fault input. This is to let the designer implement skip cycle. To the opposite, the B version goes back to operation

upon the fast fault pin release via a soft-start sequence.

### **Voltage-Controlled Oscillator**

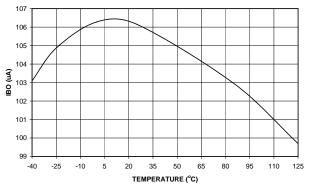

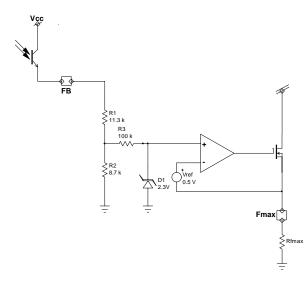

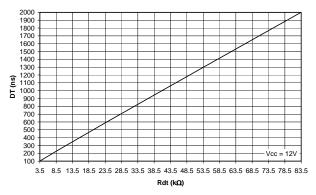

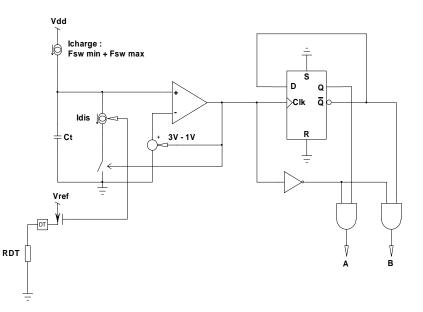

The VCO section features a high-speed circuitry allowing operation from 100 kHz up to 1 MHz. However, as a division by two internally creates the two Q and Qbar outputs, the final effective signal on output Mlower and Mupper switches between 50 kHz and 500 kHz. The VCO is configured in such a way that if the feedback pin goes up, the switching frequency also goes up. Figure 31 shows the architecture of this oscillator.

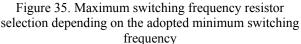

Figure 31. The simplified VCO architecture

The designer needs to program the maximum switching frequency and the minimum switching frequency. In LLC configurations, for circuits working above the resonant frequency, a high precision is required on the minimum frequency, hence the  $\pm 3\%$  specification. This minimum switching frequency is actually reached when no feedback closes the loop. It can happen during the startup sequence, a strong output transient loading or in a short-circuit condition. By installing a resistor from pin 4 to GND, the minimum frequency is set. Using the same philosophy, wiring a resistor from pin 2 to GND will set the maximum frequency excursion. To improve the circuit protection features, we have purposely created a dead zone, where the feedback loop has no action. This is typically below 1.2 V. Figure 32 details the arrangement where the internal voltage (that drives the VCO) varies between 0 and 2.3 V. However, to create this swing, the feedback pin (to which the optocoupler emitter connects), will need to swing typically between 1.2 V and 5.3 V.

Figure 32. The OPAMP Arrangement limits the VCO modulation signal between 0.5 and 2.3V

This techniques allows us to detect a fault on the converter in case the FB pin cannot rise above 0.6 V (to actually close the loop) in less than a duration imposed by the programmable timer. Please refer to the fault section for detailed operation of this mode.

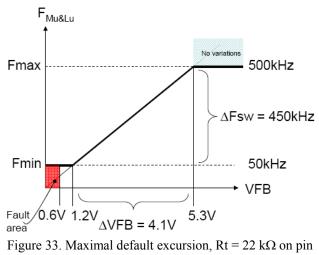

As shown on figure 32, the internal dynamics of the VCO control voltage will be constrained between 0.5 V and 2.3 V, whereas the feedback loop will drive pin 6 (FB) between 1.2V and 5.3 V. If we take the default FB pin excursion numbers, 1.2 V = 50 kHz, 5.3 V = 500 kHz, then the VCO maximum slope will be  $\frac{500k - 50k}{4.1} =$ 109.7kHz/V. Figure 33 and 34 portray the frequency evolution depending on the feedback pin voltage level in a different frequency clamp combination.

4 and Rfmax =  $1.3 \text{ k}\Omega$  on pin 2.

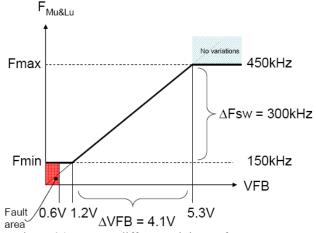

Figure 34. Here a different minimum frequency was programmed as well as a maximum frequency excursion.

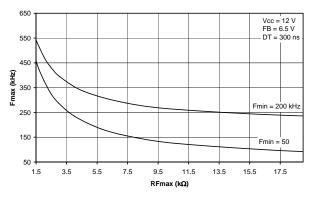

Please note that the previous small-signal VCO slope has now been reduced to 300k / 4.1 = 73 kHz / V on Mupper and Mlower outputs. This offers a mean to magnify the feedback excursion on systems where the load range does not generate a wide switching frequency excursion. Thanks to this option, we will see how it becomes possible to observe the feedback level and implement skip cycle at light loads. It is important to note that the frequency evolution does not have a real linear relationship with the feedback voltage. This is due to the deadtime presence which stays constant as the switching period changes. The selection of the three setting resistors (Fmax, Fmin deadtime) requires the usage of the selection charts displayed below:

Figure 36. Minimum switching frequency resistor selection

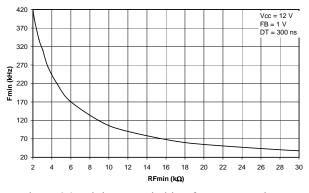

Figure 37. Dead-Time Resistor Selection

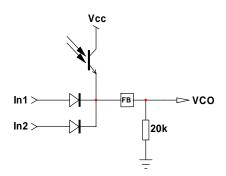

#### **ORing capability**

If for any particular reason, there is a need for a frequency variation linked to an event appearance (instead of abruptly stopping pulses), then the FB pin lends itself very well to the addition of other sweeping loops. Several diodes can easily be used perform the job in case of reaction to a fault event or to regulate on the output current (CC operation). Figure 38 shows how to do it.

Figure 38. Thanks to the FB configuration, loop ORing is easy to implement

#### **Dead-time control**

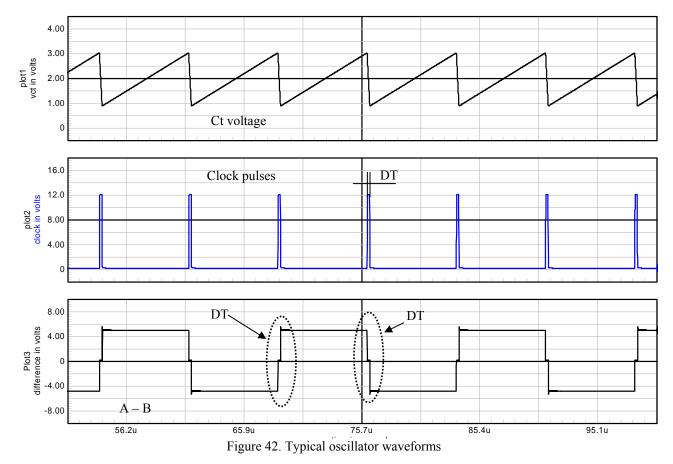

Dead-time control is an absolute necessity when the half-bridge configuration comes to play. The deadtime technique consists in inserting a period during which both high and low side switches are off. Of course, the dead-time amount differs depending on the switching frequency, hence the ability to adjust it on this controller. The option ranges between 100 ns and 2 us. The deadtime is actually made by controlling the oscillator discharge current. Figure 39 portrays a simplified VCO circuit based on figure 31.

Figure 39. Dead-time generation

During the discharge time, the clock comparator is high and un-validates the AND gates: both outputs are low. When the comparator goes back to the low level, during the timing capacitor Ct recharge time, A and B outputs are validated. By connecting a resistor RDT to ground, it creates a current whose image serves to discharge the Ct capacitor: we control the dead-time. The typical range evolves between 100 ns (RDT =  $3.5 \text{ k}\Omega$ ) and 2 us (RDT =  $83.5 \text{ k}\Omega$ ). Figure 42 shows the typical waveforms.

#### **Soft-start sequence**

In resonant controllers, a soft-start is needed to avoid suddenly applying the full current into the

resonating circuit. In this controller, a soft-start capacitor connects to pin 1 and offers a smooth frequency variation upon start-up: when the circuit starts to pulse, the VCO is pushed to the maximum switching frequency imposed by pin 2. Then, it linearly decreases its frequency toward the minimum frequency selected by a resistor on pin 4. Of course, practically, the feedback loop is suppose to take over the VCO lead as soon as the output voltage has reached the target. If not, then the minimum switching frequency is reached and a fault is detected on the feedback pin (typically below 600mV). Figure 40 depicts a typical frequency evolution with soft-start.

Please note that the soft-start will be activated in the following conditions:

- A startup sequence

- During auto-recovery burst mode

- A brown-out recovery

- A temperature shutdown recovery

The fast fault input undergoes a special treatment. Since we want to implement skip cycle through the fast fault input on the NCP1396A, we cannot activate the soft-start every time the feedback pin stops the operations in low power mode. Therefore, when the fast fault pin is released, no soft-start occurs to offer the best skip cycle behavior. However, it is very possible to combine skip cycle and true fast fault input, e.g. via ORing diodes driving pin 6. In that case, if a signal maintains the fast fault input high long enough to bring the feedback level down (that is to say below 0.6 V) since the output voltage starts to fall down, then the soft-start is activated after the release of the pin. In the B version tailored to operate from an auxiliary 12 V power supply, the soft-start is always activated upon the fast fault input release, whatever the feedback condition is.

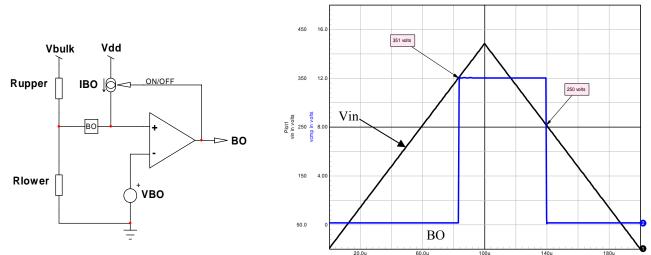

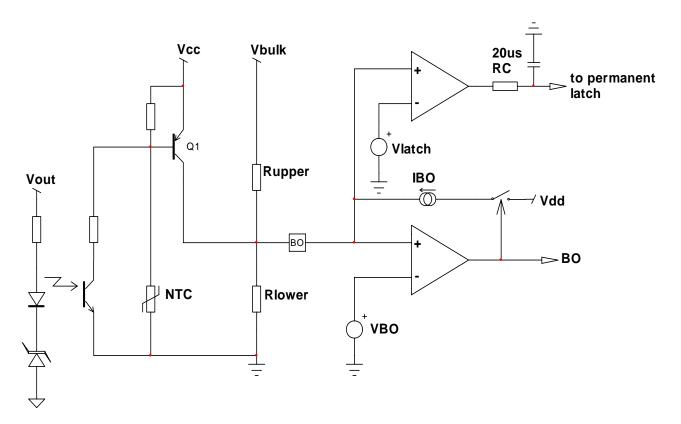

### **Brown-Out protection**

The Brown-Out circuitry (BO) offers a way to protect the resonant converter from low DC input voltages. Below a given level, the controller blocks the output pulses, above it, it authorizes them. The internal circuitry, depicted by figure 43, offers a way to observe the high-voltage (HV) rail. A resistive divider made of Rupper and Rlower, brings a portion of the HV rail on pin 5. Below the turn-on level, the  $27\mu$ A current source IBO is off. Therefore, the turn-on level solely depends on the division ratio brought by the resistive divider.

Figure 43. The internal brown-out configuration with an offset current source

To the contrary, when the internal BO signal is high (Mlower and Mupper pulse), the IBO source is activated and creates a hysteresis. As a result, it becomes possible

to select the turn-on and turn-off levels via a few lines of algebra:

IBO is off

$$V(+) = Vbulk1 \times \frac{Rlower}{Rlower + Rupper}$$

eq. 1

IBO is on

$$V(+) = Vbulk 2 \times \frac{Rlower}{Rlower + Rupper} + IBO \times \left(\frac{Rlower \times Rupper}{Rlower + Rupper}\right)$$

eq. 2

We can now extract Rlower from equation 1 and plug it into equation 2, then solve for Rupper:

$$Rupper = Rlower \times \frac{Vbulk1 - VBO}{VBO}$$

$$Rlower = VBO \times \frac{Vbulk1 - Vbulk2}{IBO \times (Vbulk1 - VBO)}$$

If we decide to turn-on our converter for Vbulk1 equals 350V and turn it off for Vbulk2 equals 250V, then we obtain:

Rupper =  $1M\Omega$

Rlower =  $2.86k\Omega$

The bridge power dissipation is  $400^2 / 1.00286M\Omega = 160$ mW when front-end PFC stage delivers 400V.

Figure 44 simulation result confirms our calculations.

### Latch-off protection

There are some situations where the converter shall be fully turned-off and stay latched. This can happen in presence of an over-voltage (the feedback loop is drifting) or when an over temperature is detected. Thanks to the addition of a comparator on the BO pin, a simple external circuit can lift up this pin above VLATCH (4 V typical) and permanently disable pulses. The Vcc needs to be cycled down below 6.5 V typically to reset the controller.

Figure 45. Adding a comparator on the BO pin offers a way to latch-off the controller

On figure 45, Q1 is blocked and does not bother the BO measurement as long as the NTC and the optocoupler are not activated. As soon as the secondary optocoupler senses an OVP condition, or the NTC reacts to a high ambient temperature, Q1 base is brought to ground and the BO pin goes up, permanently latching off the controller.

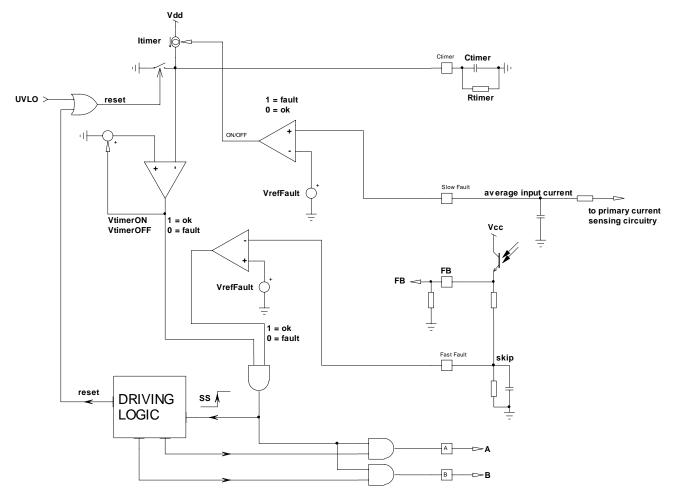

# **Protection circuitry**

This resonant controller differs from competitors thanks to its protection features. The device can react to various inputs like:

- *Fast events input*: like an over-current condition, a need to shut down (sleep mode) or a way to force a controlled burst mode (skip cycle at low output power): as soon as

the input level exceeds 1V typical, pulses are immediately stopped. When the input is released, the controller performs a clean startup sequence including a soft-start period.

-Slow events input: this input serves as a delayed shutdown, where an event like a transient overload does not immediately stopped pulses but start a timer. If the event duration lasts longer than what the timer imposes, then all pulses are disabled. The voltage on the timer capacitor (pin 3) starts to decrease until it reaches 1V. The decrease rate is actually depending on the resistor the user will put in parallel with the capacitor, giving another flexibility during design.

Figure 46 depicts the architecture of the fault circuitry.

Figure 46. This circuit combines a slow and fast input for improved protection features.

### **Slow input**

On this circuit, the slow input goes to a comparator. When this input exceeds 1V typical, the current source Itimer turns on, charging the external capacitor Ctimer. If the fault duration is long enough, when Ctimer voltage reaches the VtimerON level (4V typical), then all pulses are stopped. If the fault input signal is still present, then the controller permanently stays off and the voltage on the timer capacitor does not move (Itimer is on and the voltage is clamped to 5V). If the fault input signal is removed (because pulses are off for instance), Itimer turns off and the capacitor slowly discharges to ground via a resistor installed in parallel with it. As a result, the designer can easily determine the time during which the power supply stays locked by playing on Rtimer. Now, when the timer capacitor voltage reaches 1V typical (VtimerOFF), the comparator instructs the internal logic to issues pulses as on a clean soft-start sequence (soft-start is activated). Please note that the

discharge resistor can not be lower than 4V / Itimer otherwise the voltage on Ctimer will not reach the turn-off voltage of 4V.

In both cases, when the fault is validated, both outputs Mlower and Mupper are internally pulled down to ground.

On figure 46 example, a voltage proportional to primary current, once averaged, gives an image of the input power in case Vin is kept constant via a PFC circuit. If the output loading increases above a certain level, the voltage on this pin will pass the 1V threshold and start the timer. If the overload stays there, after a few tens of milliseconds, switching pulses will disappear and a protective auto-recovery cycle will take place. Adjusting the resistor R in parallel with the timer capacitor will give the flexibility to adjust the fault burst mode.

Figure 47. A resistor can easily program the capacitor discharge time

Figure 48. Skip cycle can be implemented via two resistors on the FB pin to the Fast fault input.

## **Fast input**

The fast input is not affected by a delayed action. As soon as its voltage exceeds 1V typical, all pulses are off and maintained off as long as the fault is present. When the pin is released, pulses come back and the softstart is activated.

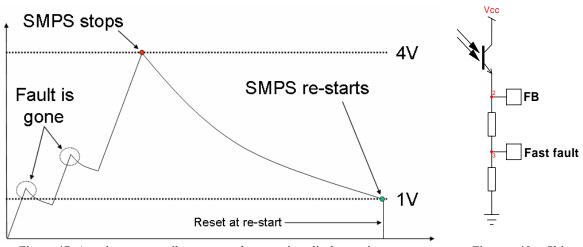

Thanks to the low activation level of 1V, this pin can observe the feedback pin via a resistive divided and thus implement skip cycle operation. The resonant converter can be designed to lose regulation in light load conditions, forcing the FB level to increase. When it reaches the programmed level, it triggers the fast fault input and stops pulses. Then Vout slowly drops, the loop reacts by decreasing the feedback level which, in turn, unlocks the pulses, Vout goes up again and so on: we are in *skip cycle* mode.

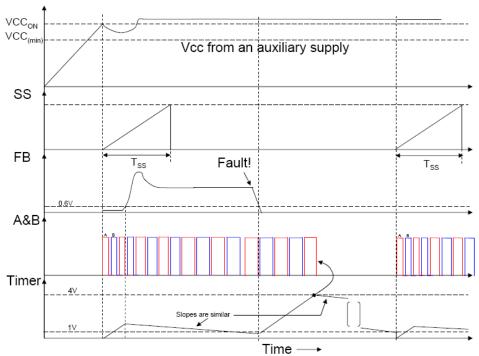

### Startup behaviour

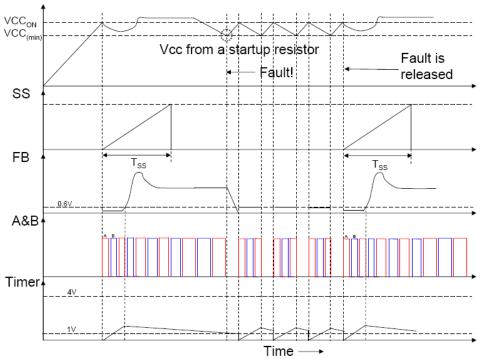

When the Vcc voltage grows-up, the internal current consumption is kept to Istrup, allowing to crankup the converter via a resistor connected to the bulk capacitor. When Vcc reaches the VccON level, output Mlower goes high first and then output Mupper. This sequence will always be the same whatever triggers the pulse delivery: fault, OFF to ON etc... Pulsing the output Mlower high first gives an immediate charge of the bootstrap capacitor. Then, the rest of pulses follow, delivered at the highest switching value, set by the resistor on pin 2. The soft-start capacitor ensures a smooth frequency decrease to either the programmed minimum value (in case of fault) or to a value corresponding to the operating point if the feedback loop closes first. Figure 49 shows typical signals evolution at power on.

Figure 49. At power on, output A is first activated and the frequency slowly decreases via the soft-start capacitor

Figure 49 depicts an auto-recovery situation, where the timer has triggered the end of output pulses. In that case, the Vcc level was given by an auxiliary power supply, hence its stability during the hiccup. A similar situation can arise if the user selects a more traditional startup method, with an auxiliary winding. In that case, the VCC(min) comparator stops the output pulses whenever it

is activated, that is to say, when Vcc falls below 10V typical. At this time, the Vcc pin still receives its bias current from the startup resistor and heads toward VCC<sub>ON</sub> via the Vcc capacitor. When the voltage reaches VCC<sub>ON</sub>, a standard sequence takes place, involving a soft-start. Figure 50 portrays this behavior.

Figure 50. When the Vcc is too low, all pulses are stopped until Vcc goes back to the startup voltage

As described in the data-sheet, two startup levels  $VCC_{ON}$  are available, via two circuit versions. The NCP1396 features sufficient hysteresis (3V typically) to allow a classical startup method with a resistor connected to the bulk capacitor. Then, at the end of the startup sequence, an auxiliary winding is supposed to take over the controller supply voltage. To the opposite, for applications where the resonant controller is powered from a standby power supply, the startup level is 10V typically and allows for the direct a connection from a

12V source. Thanks to this NCP1396B, simple ON/OFF operation is therefore feasible.

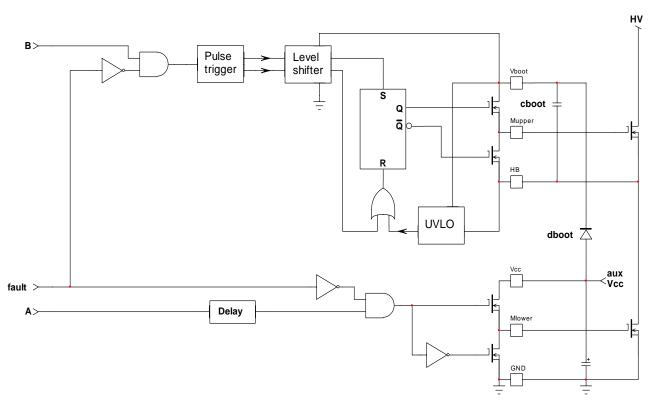

# The high-voltage driver

The driver features a traditional bootstrap circuitry, requiring an external high-voltage diode for the capacitor refueling path. Figure 51 shows the internal architecture of the high-voltage section.

Figure 51. The Internal High-voltage Section of the NCP1396

The device incorporates an upper UVLO circuitry that makes sure enough Vgs is available for the upper side MOSFET. The B and A outputs are delivered by the internal logic, as figure 46 testifies. A delay is inserted in the lower rail to ensure good matching between these propagating signals. As stated in the maximum rating section, the floating portion can go up to 600VDC and makes the IC perfectly suitable for offline applications featuring a 400V PFC front-end stage.

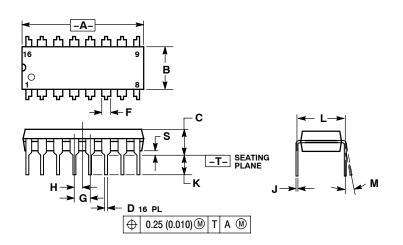

#### PACKAGE DIMENSIONS

PDIP-16 **P SUFFIX** CASE 648-08 **ISSUE T**

- NOTES: 1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH.

- DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL. DIMENSION B DOES NOT INCLUDE З. 4.

- MOLD FLASH.

- 5. ROUNDED CORNERS OPTIONAL.

|     | INC   | HES   | MILLIMETERS |       |  |

|-----|-------|-------|-------------|-------|--|

| DIM | MIN   | MAX   | MIN         | MAX   |  |

| Α   | 0.740 | 0.770 | 18.80       | 19.55 |  |

| в   | 0.250 | 0.270 | 6.35        | 6.85  |  |

| С   | 0.145 | 0.175 | 3.69        | 4.44  |  |

| D   | 0.015 | 0.021 | 0.39        | 0.53  |  |

| F   | 0.040 | 0.70  | 1.02        | 1.77  |  |

| G   | 0.100 | BSC   | 2.54 BSC    |       |  |

| н   | 0.050 | BSC   | 1.27 BSC    |       |  |

| J   | 0.008 | 0.015 | 0.21        | 0.38  |  |

| К   | 0.110 | 0.130 | 2.80        | 3.30  |  |

| L   | 0.295 | 0.305 | 7.50        | 7.74  |  |

| М   | 0 °   | 10 °  | 0 °         | 10 °  |  |

| S   | 0.020 | 0.040 | 0.51        | 1.01  |  |

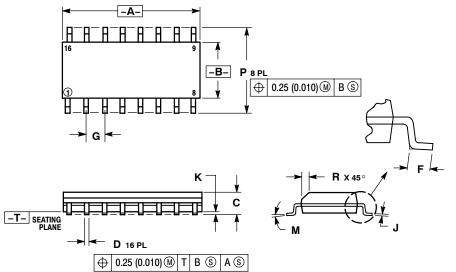

SO-16 **D SUFFIX** CASE 751B-05 ISSUE J

NOTES:

- NO IES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006)

DED DIVENSION.

- 5.

MAXIMUM MOLD PHOTHUSIUM 0.15 (0.000) PER SIDE. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|             | MILLIN                      | IETERS                      | INCHES                         |                                |  |

|-------------|-----------------------------|-----------------------------|--------------------------------|--------------------------------|--|

| DIM         | MIN                         | MAX                         | MIN                            | MAX                            |  |

| Α           | 9.80                        | 10.00                       | 0.386                          | 0.393                          |  |

| В           | 3.80                        | 4.00                        | 0.150                          | 0.157                          |  |

| C           | 1.35                        | 1.75                        | 0.054                          | 0.068                          |  |

| D           | 0.35                        | 0.49                        | 0.014                          | 0.019                          |  |

| F           | 0.40                        | 1.25                        | 0.016                          | 0.049                          |  |

| G           | 1.27                        | BSC                         | 0.050 BSC                      |                                |  |

| J           | 0.19                        | 0.25                        | 0.008                          | 0.009                          |  |

| K           | 0.10                        | 0.25                        | 0.004                          | 0.009                          |  |

| Μ           | 0 °                         | 7°                          | 0 °                            | 7°                             |  |

| Р           | 5.80                        | 6.20                        | 0.229                          | 0.244                          |  |

| R           | 0.25                        | 0.50                        | 0.010                          | 0.019                          |  |

| K<br>M<br>P | 0.19<br>0.10<br>0 °<br>5.80 | 0.25<br>0.25<br>7 °<br>6.20 | 0.008<br>0.004<br>0 °<br>0.229 | 0.009<br>0.009<br>7 °<br>0.244 |  |

Note: The product described herein (NCP1396A/B), is covered by U.S. patent: 6,097, 075; 7176723; 6,362, 067. There may be some other patent pending.

ON Semiconductor and I are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specification scan and do vary in different applications special, consequential or incidental damages. "Typical" parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products for any softened for explication in which the failure of the SCILLC coduct could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

ON Semiconductor Website: www.onsemi.com

Sales Representative

Order Literature: http://www.onsemi.com/orderlit For additional information, please contact your local

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850

NCP1396/D

#### NCP1396A, NCP1396B